mips assembly instruction은 크게 세가지로 나뉜다.

- 산술/논리 연산 명령어 (add, addi, sub, and, or, sll, srl 등)

- 메모리 접근 명령어 (lw, sw 등)

- 분기 명령어 (j, jr, jal, beq, bne 등)

이렇게 다양한 명령어들은 각각의 format에 따라 다른 방식으로 기계어로 표현되는데,

(명령어의 산술종류와 format은 관련이 없다. 같은 덧셈연산이라고 해도 add는 r-format, addi는 i-format이다.)

이 중에 R-format, I-format, J-format에 따라 어셈블리 명령어를 기계어로 바꾸는 어셈블 연습을 해보자.

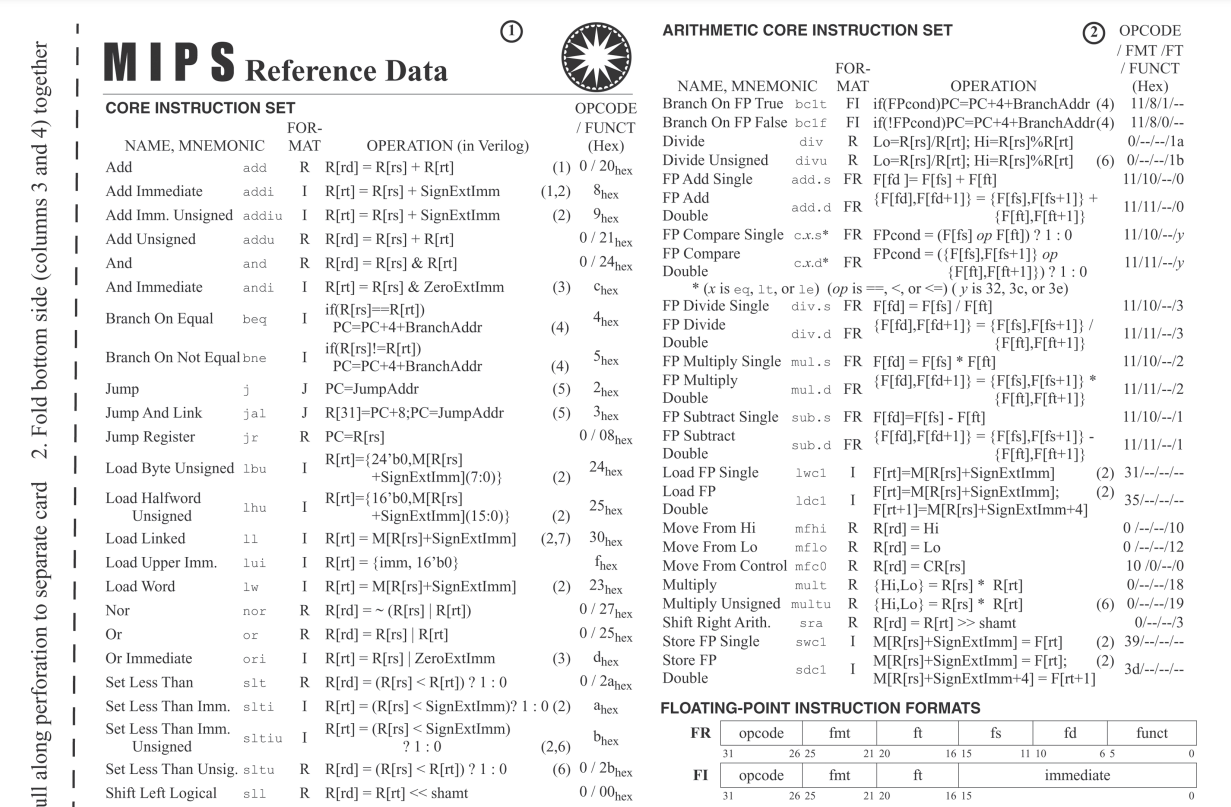

각각의 instruction이 어떤 포맷인지는 다음 opcode table을 보면 빠르게 확인할 수 있다!

opcode가 00이면 R format이고, 화살표를 따라가면 function field를 확인할 수 있다.

그렇지 않으면 I 또는 J format 이다.

아니면 컴퓨터구조 및 설계 책의 부록인 레퍼런스 카드를 통해서 좀 더 명확하게 확인할 수 있다.

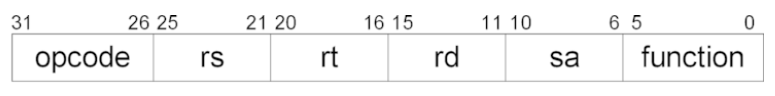

1. R format (add, addu, and, or, slt, sll, srl 등)

맨앞의 6bits는 op코드 자리 (r format에서는 전부 000000)이다.

rs/rt에는 source가 되는 레지스터 두개의 번호가 각각 5bits씩 들어간다.

rd에는 destination이 되는 레지스터의 번호가 5bits 들어간다.

sa는 shift amount (5bits)인데, sll(shift left logical)이나 srl(shift right logical)처럼 시프트연산을 하는 경우에 써준다.

마지막은 function field로 각 instruction이 구분되는 function code를 6bits 써준다.

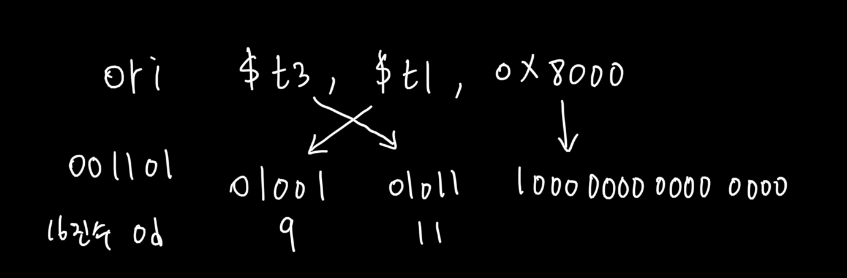

2. I format (addi, andi, beq, bne 등)

맨앞의 6bits는 op코드 자리이다. (i format에서는 명령어에 따라 그 값이 다르다.)

rs에는 source가 되는 하나의 레지스터 번호가 5bits 들어간다.

rt에는 destination이 되는 레지스터의 번호가 5bits 들어간다.

맨 뒤의 immediate field에는 상수필드값이 16bits 들어간다.

그런데 여기서 immediate field가 16bits이기 때문에 나중에 이 값이 ALU(산술논리연산자)로 들어갈때는 32bits로 확장되어야 하는데, 논리연산일 경우 상위비트를 무조건 0으로 채우고(zero extension), 산술연산일 경우 음수인지 양수인지에 따라 다르게 확장하는 sign extension을 진행한다.

3. J format (j, jal 등)

맨 앞의 6bits는 op코드 자리이다. (j format에서는 명령어에 따라 그 값이 다르다.)

그 뒤의 26bits에는 이동할 BTA(branch target address)값이 들어가게 된다.

참고로 j와 jal는 똑같이 특정 label로 이동하는 명령어인데, 차이는 jal가 해당 레이블로 이동한 후 바로 다음 instruction의 메모리 주소를 $ra($31, return address)에 저장해둔다는 점이다.

특정 함수가 끝나고 바로 다음 instruction으로 리턴해주기 위해 해당 기능이 존재하는 것이다.

그런데 같은 format이라고 해도 instruction에 따라 기계어로 변환하는 방법이 세부적으로는 약간 다른 경우도 있다.

그런 경우는 나중에 추가글로 작성하도록 하겠다.

'컴퓨터 구조' 카테고리의 다른 글

| mips pipeline hazard (컴퓨터구조 2022-2학기) (0) | 2022.11.26 |

|---|---|

| mips pipeline control (컴퓨터구조 2022-2학기) (0) | 2022.11.25 |

| mips pipeline datapath (컴퓨터구조 2022-2학기) (0) | 2022.11.24 |