processor가 pipelining을 하려면

- load를 여러개의 sub-task로 나누어야 함

- 각 sub-task는 1-clock cycle에 수행됨 (즉 명령어 한개가 여러 clock cycle에 수행됨.)

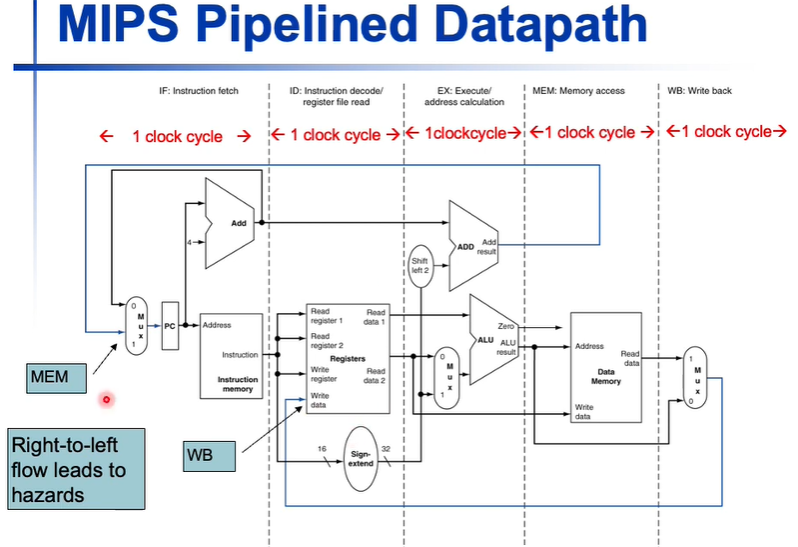

MIPS pipeline의 5 stage

1. IF = 메모리로부터 instruction을 fetch하는 스테이지

2. ID = fetch된 instruction을 decode하고, 필요한 레지스터 값을 읽어오는 스테이지

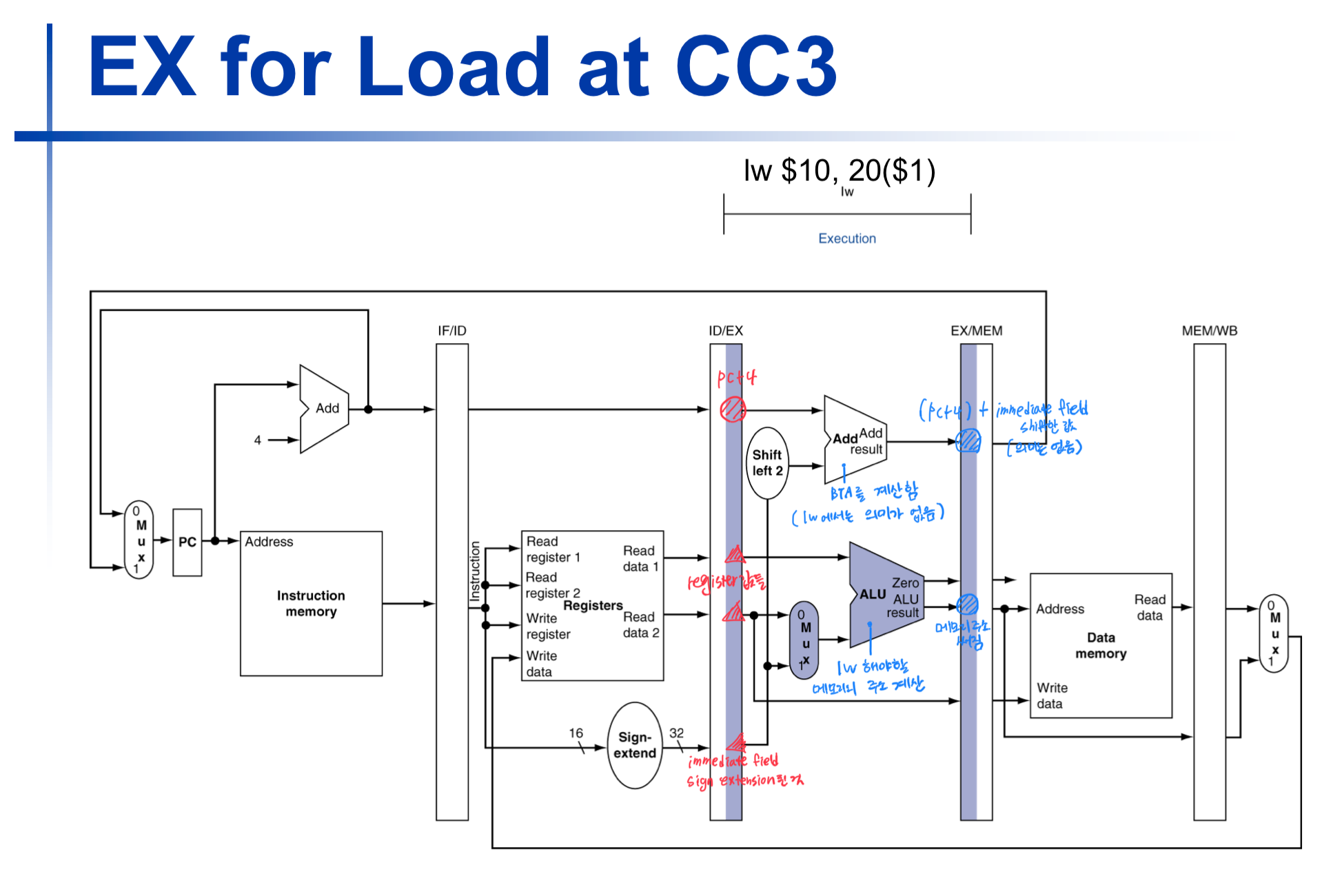

3. EX = instruction을 수행하거나, 메모리의 주소를 계산하는(lw, sw 등) 스테이지

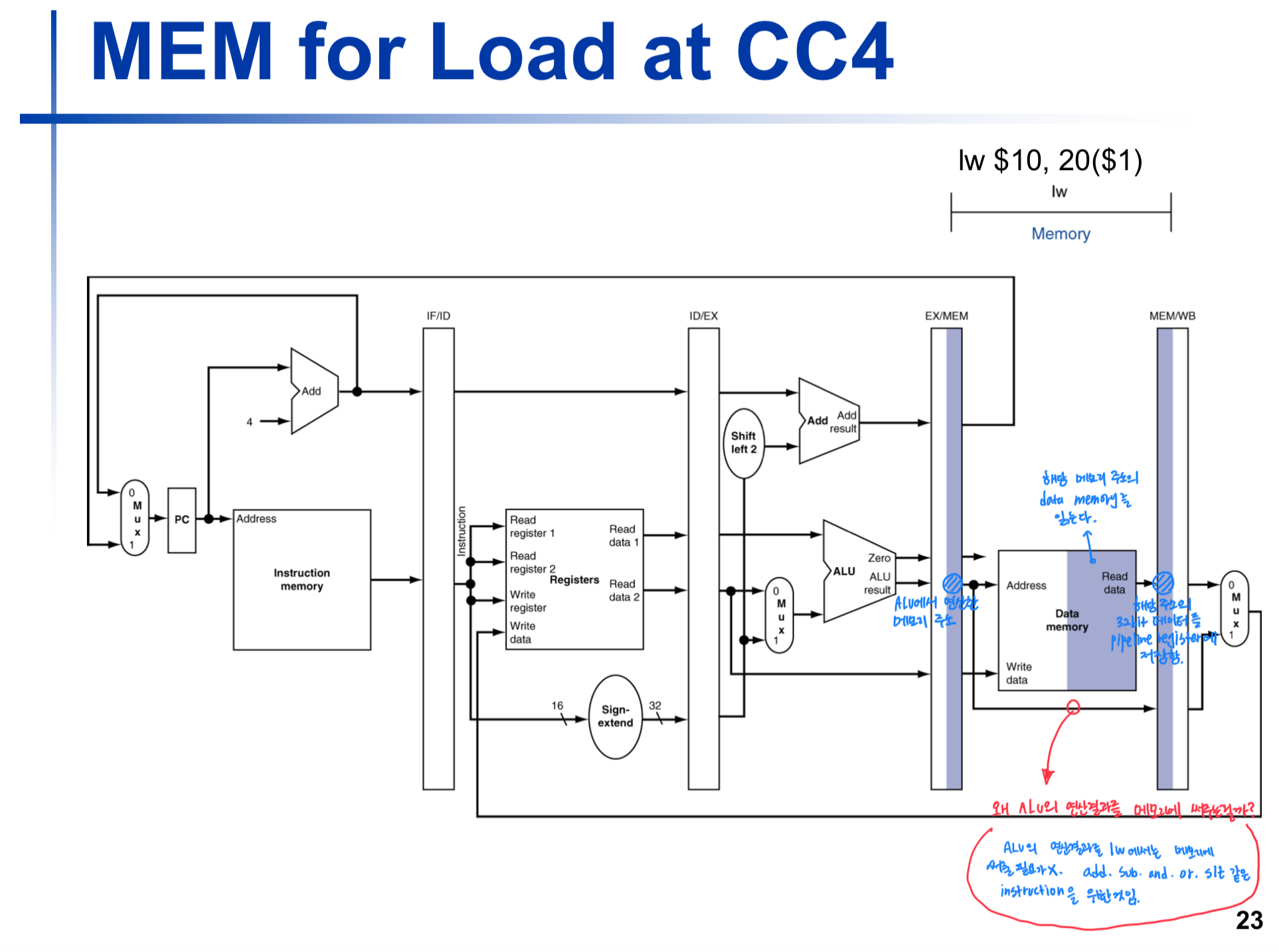

4. MEM = 데이터메모리에 access해서 여기에 값을 쓰거나 읽는 스테이지

5. WB = 연산의 결과를 레지스터 파일에 쓰는 스테이지

위의 스테이지들은 각각 한 사이클에 수행되므로, instruction 하나를 수행하기 위해서는 총 5사이클이 필요한 것이다.

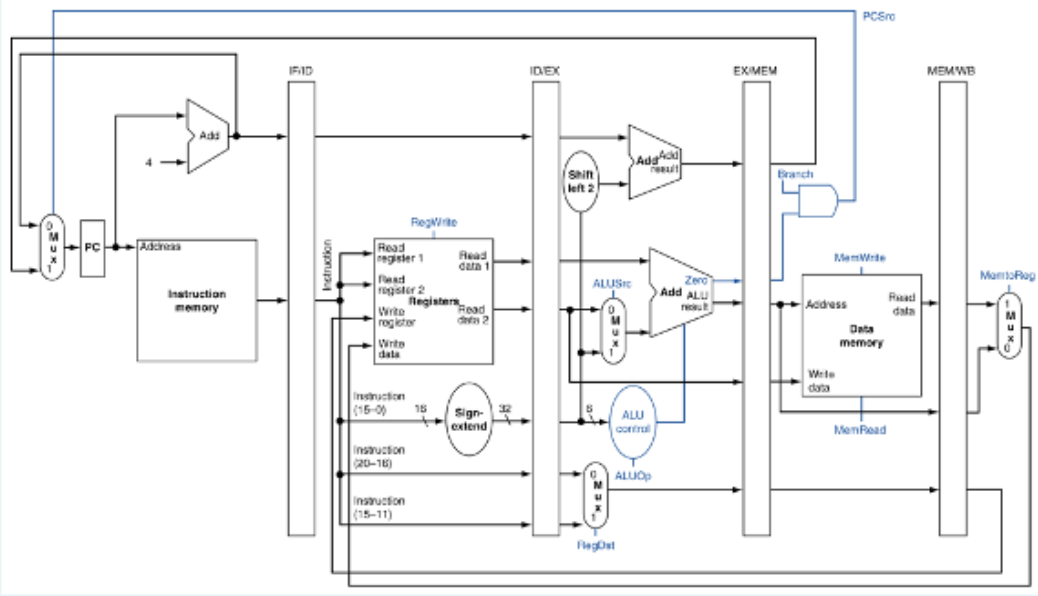

- 밑부분의 파란 화살표처럼 데이터가 거꾸로 흐르게 되면 이것은 hazard가 되어서 별도로 해결해줘야한다. (이후 작성예정)

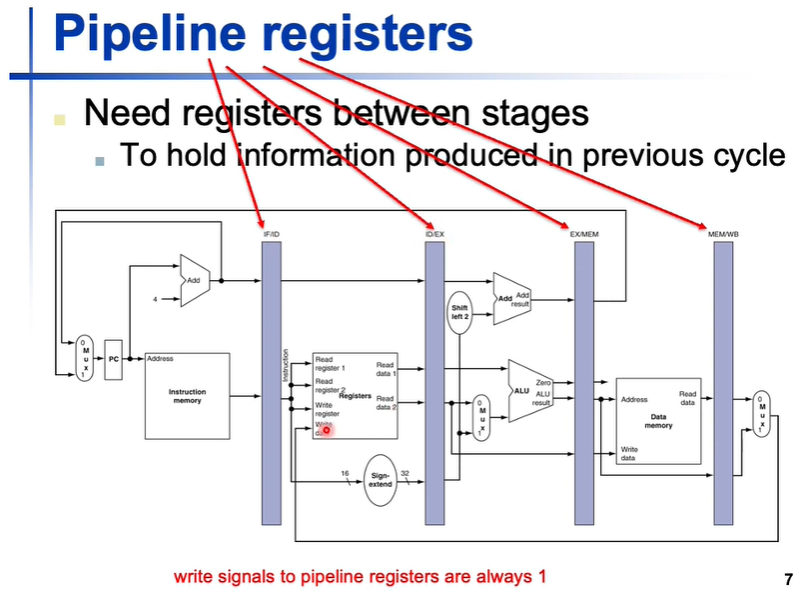

- 한 사이클이 끝나고 나서 다음 사이클을 위해서는 끝난 사이클의 값이 어딘가 저장되어있다가 와야한다.

synchronous digital 회로의 동작

클락사이클동안 조합회로에서 입력신호에 대한 출력신호를 만든다.

combinational 회로의 input은 state element의 output이고, output은 state element의 input이다.

그니까 간단히 말해서 사이클이 끝나면 이 값을 저장해둘 state element가 필요하고, 이 역할을 해주는것이 pipeline register이다.

매 clock cycle이 끝날때마다 값이 써질 수 있도록 pipeline register의 write signal은 항상 1이 된다.

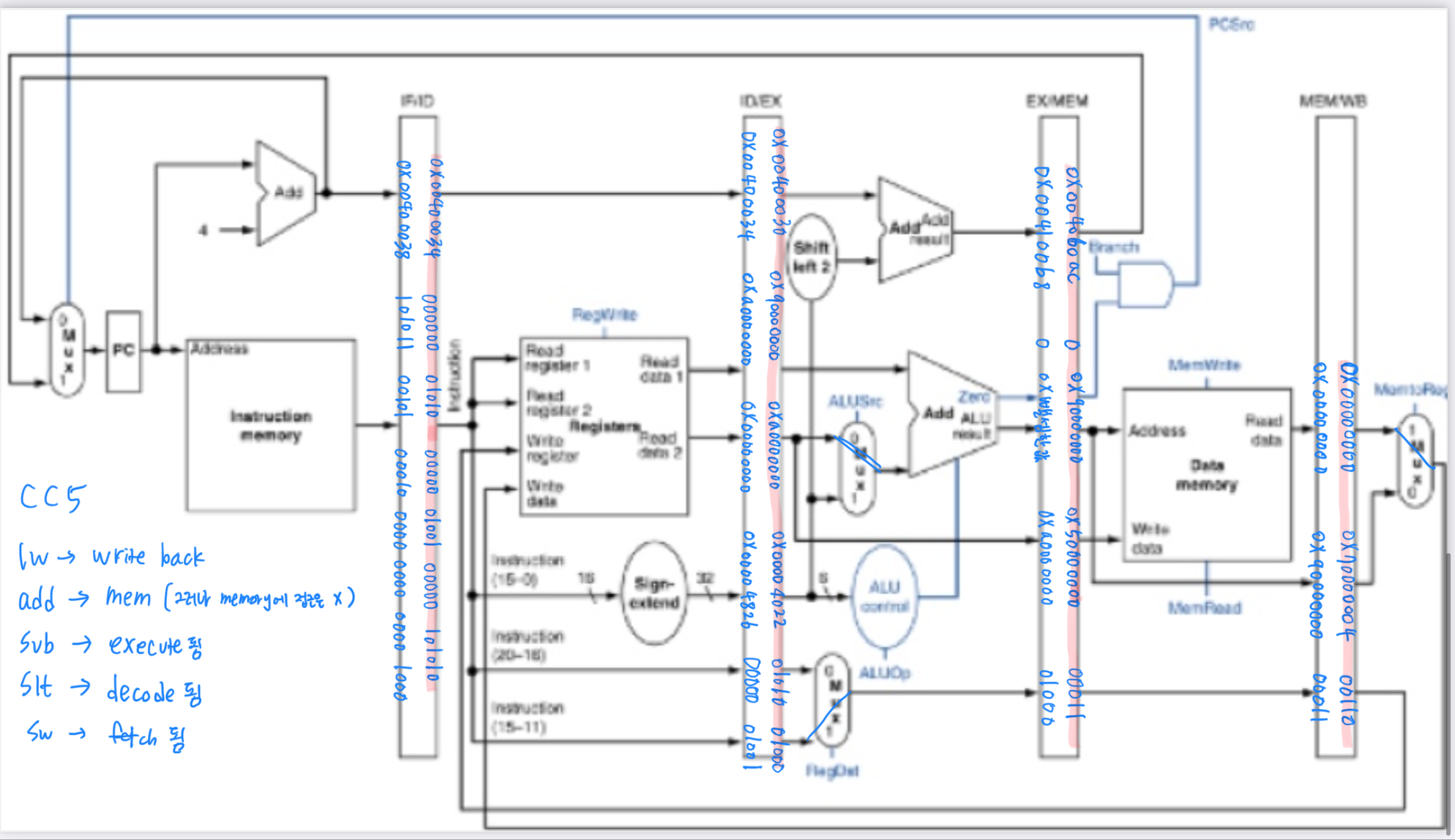

multi cycle에서는 한 사이클에 여러가지 일들이 일어난다. CC5의 경우를 살펴보면 lw instruction이 WB stage에 있는 동시간에 sub는 MEM stage, add는 EX stage, 두번째 lw는 ID stage, 마지막 add는 IF stage에 있게된다.

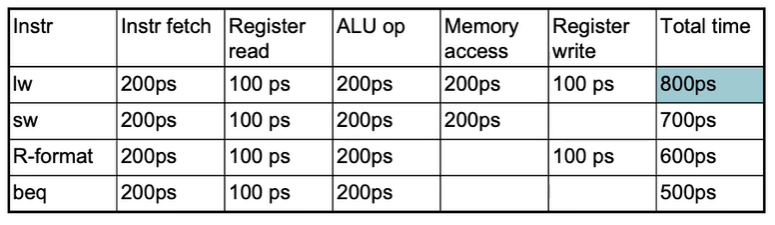

pipeline processor의 cycle time

- 레지스터를 읽거나 쓰는데에 100ps

- 메모리에 access하거나, ALU에서 입출력이 만들어지는데에 200ps

그래서 다른 딜레이를 무시한다면 clock cycle time은 200ps로 통일하면 된다.

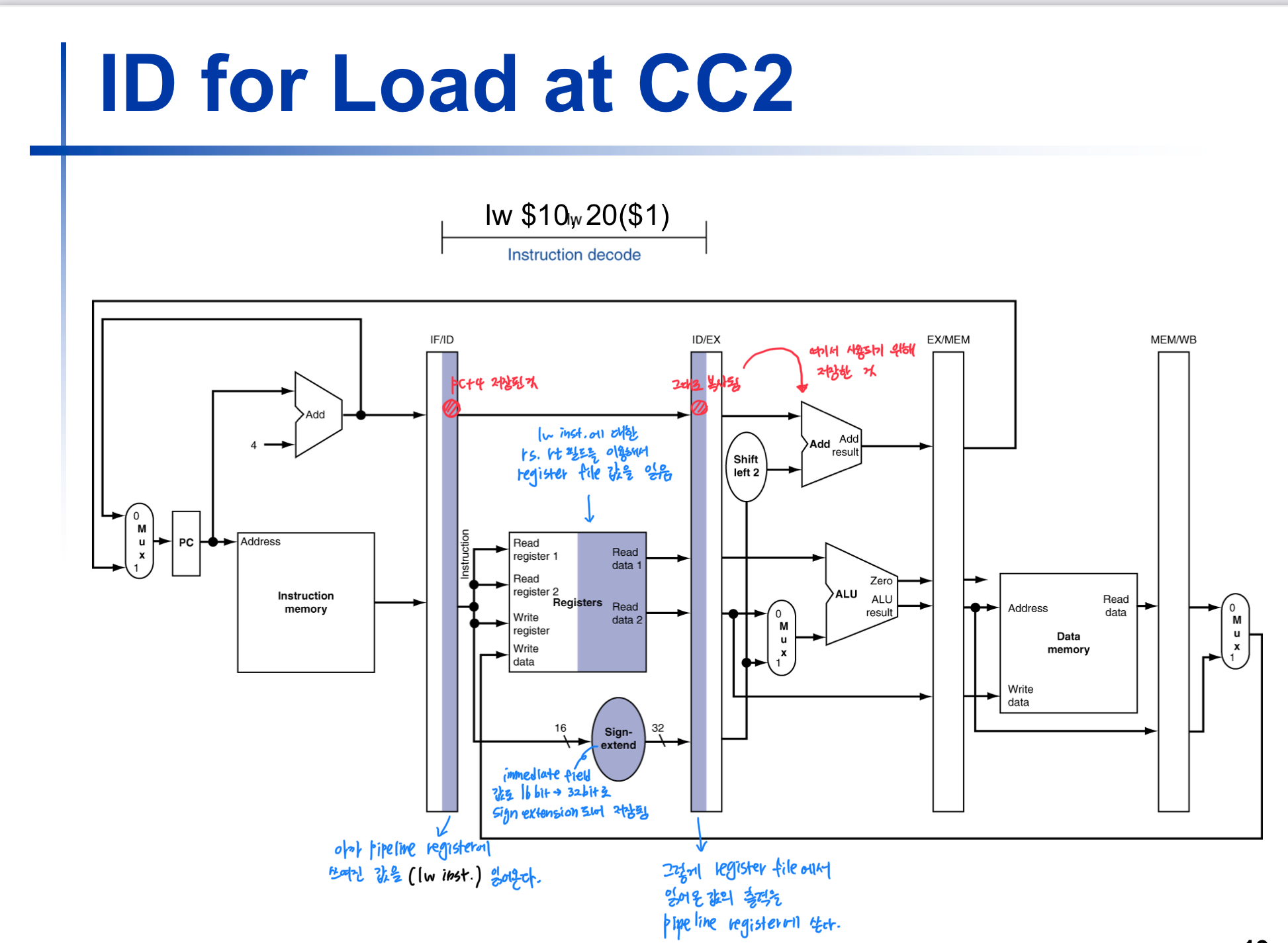

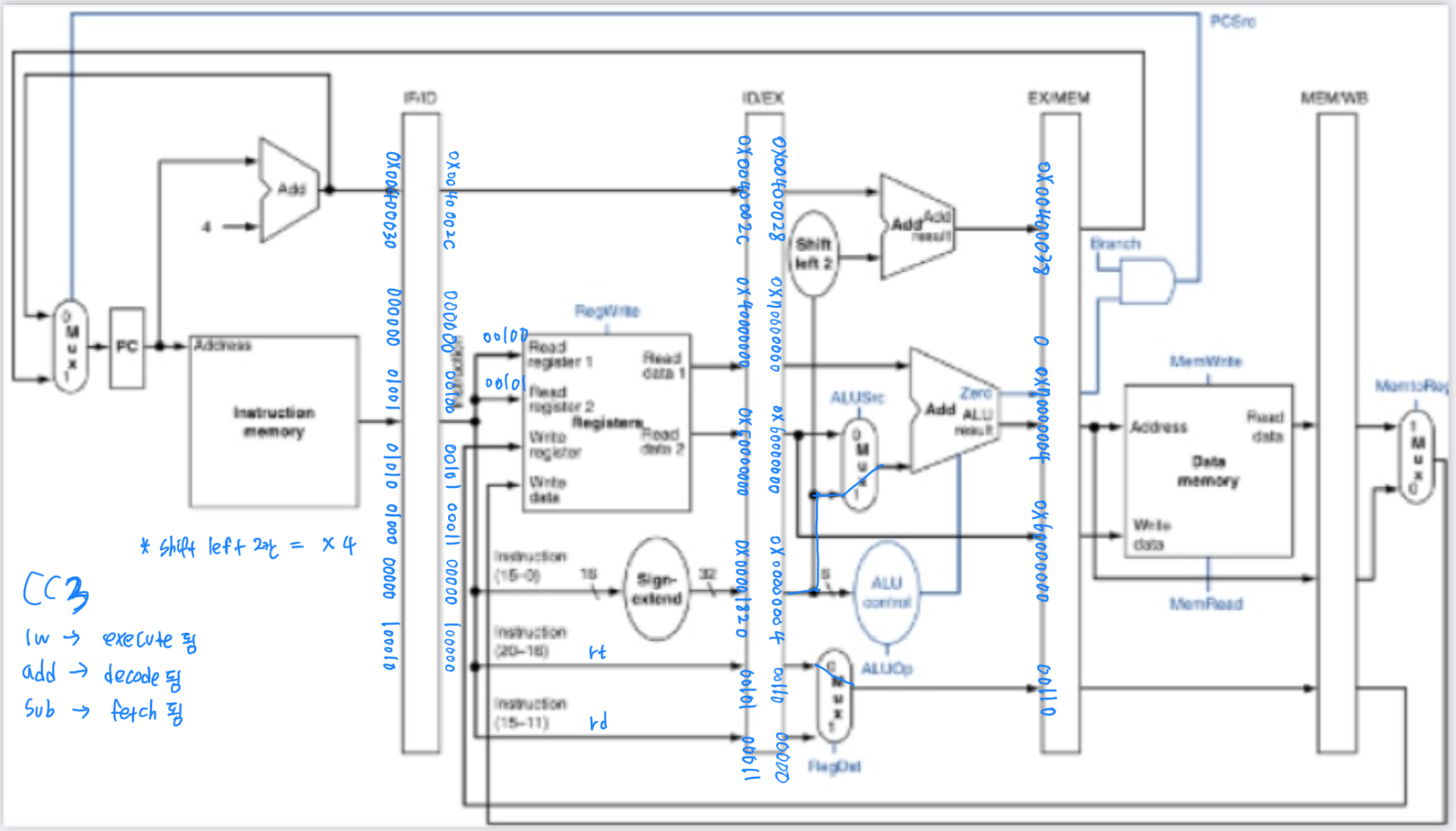

clock cycle에 따른 pipeline 데이터 살펴보기

위 사진의 필기에 언급된 문제를 해결하는 방법은 ID/EX 파이프라인부터 5비트를 늘리고, 거기에 destination register번호를 써주는 것이다. (그리고 이걸 나중에 write register번호로 사용함)

아래 사진의 필기를 참고하면 무슨 뜻인지 더 잘 알수있다!

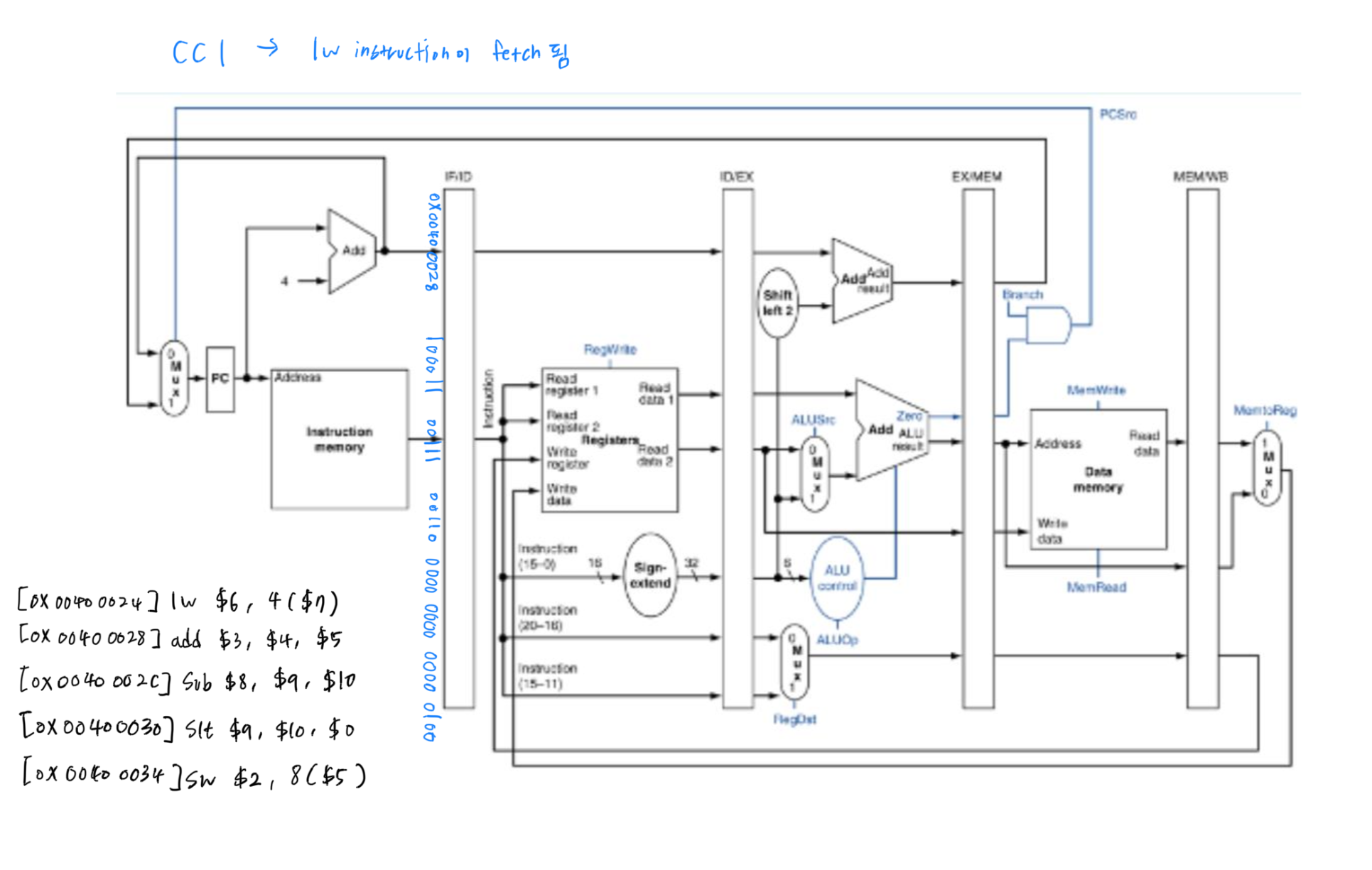

파이프라인 예제 풀이 (퀴즈 14번 풀이)

- 문제

다음 그림과 같은 회로에서

instruction memory 의 내용은 다음과 같다.

[0x00400024] lw $6, 4($7)

[0x00400028] add $3,$4,$5

[0x0040002c] sub $8,$9,$10

[0x00400030] slt $9, $10, $0

[0x00400034] sw $2, 8($5)

register file 의 내용은 다음과 같다.

$0 : 0x00000000

$1 : 0x10000000

$2 : 0x20000000

$3 : 0x30000000

$4 : 0x40000000

$5 : 0x50000000

$6 : 0x60000000

$7 : 0x70000000

$8 : 0x80000000

$9 : 0x90000000

$10 : 0xa0000000

Data Memory 의 내용은 모두 0 이다.

이 회로는 rising edge triggered 회로이고 c1 일 때 PC 의 값은 0x00400024 였다.

c2 일 때 (c1 으로부터 4번째 clock cycle 이 끝나기 직전)

1. IF/ID pipeline register

2. ID/EX pipeline register

3. EX/MEM pipeline register

4. MEM/WB pipeline register의 값을 16진수로 쓰시오. (띄어쓰기는 하지말고 0x 로 시작할 것)

그림의 EX/MEM pipeline register 의 길이는 4의 배수가 아니므로 16진수로 표현하기 위해 bit1, bit0 의 값은 모두 0으로 가정하여 추가한 후 16진수로 표현할 것.

* 레지스터의 값이라는 것은 현재 저장되어 출력되는 값을 뜻합니다. 아직 저장되지 않은 값은 레지스터의 값이 아닙니다.

- 풀이

(cc1부터 cc5까지 파이프라인에 쓰여지는 데이터들을 나타냄. 0x로 시작하면 16진수, 그렇지 않으면 2진수이고 16진수로 답을 구하는 과정에서 4비트 쌍이 맞지 않을 경우, 뒤에 0을 필요한 만큼 추가하여 16진수로 나타내준다.)

* 본 포스팅은 국민대학교 소프트웨어학부 컴퓨터구조 2022-2학기 수업 내용에 대해 정리한 것입니다. 참고 자료는 임은진 교수님의 수업 자료이고, 참고 도서는 한티미디어 컴퓨터 구조 및 설계 6판입니다.

'CS > 컴퓨터 구조' 카테고리의 다른 글

| mips pipeline hazard (컴퓨터구조 2022-2학기) (0) | 2022.11.26 |

|---|---|

| mips pipeline control (컴퓨터구조 2022-2학기) (0) | 2022.11.25 |

| MIPS 어셈블리 명령어 (R,I,J format) 기계어로 표현하기 (1) | 2022.10.25 |