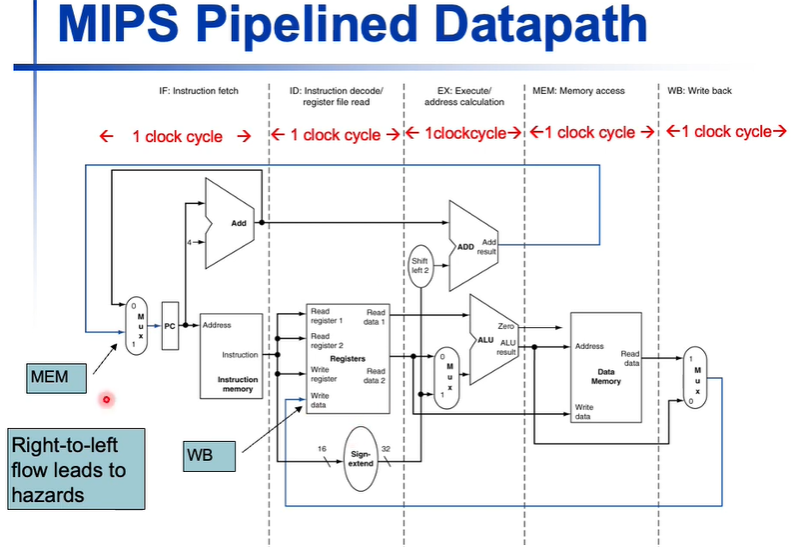

pipeline hazard 파이프라인 프로세서에서 명령어의 수행이 끝나기 전에 다른 명령어의 수행이 시작되기 때문에 생기는 문제! 기본적으로 pipeline stall을 하는 방법으로 해결할 수 있지만 (새 instruction을 fetch하지 않고 한 싸이클 쉬는것) stall이 많을수록 프로세서의 performance는 떨어지게 됨. 따라서 다양한 해결방법을 통해 stall을 최소화해야 한다. 1. Structural hazard pipeline에서 한 사이클동안 여러개의 instruction이 수행되어서 생기는 구조적 문제! 서로 다른 instruction이 같은 리소스를 사용할때 conflict가 발생한다. instruction memory와 data memory를 하드웨어상에서 분리해서 해결할..